fpga开发流程层次思想Latch

FPGA Verilog 开发流程

- 使用工具 vivado、 notepad++、 viso

流程:

- 绘制框图、真值表、波形图

- 创建vivado项目,创建.v文件

- 创建tb.v仿真文件

- 模拟仿真

- 仿真验证通过后,绑定管脚,上板验证

层次化设计思想:

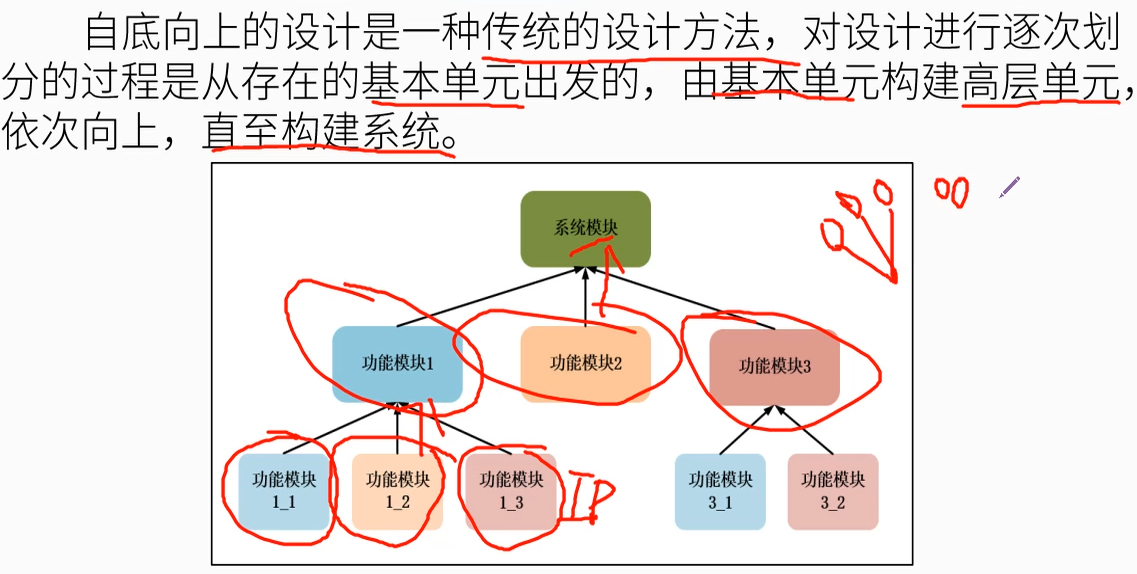

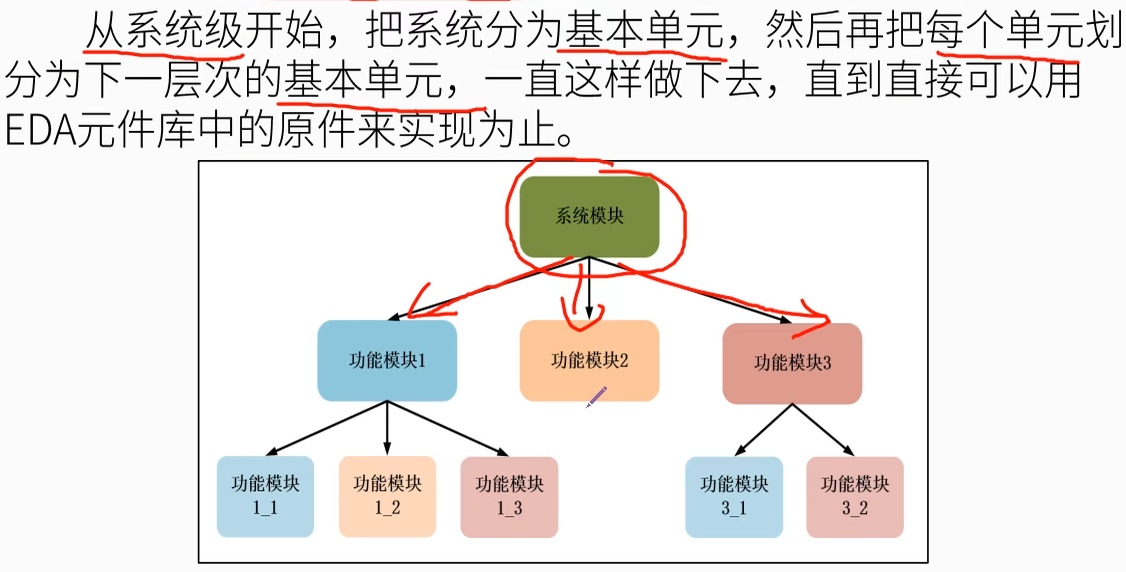

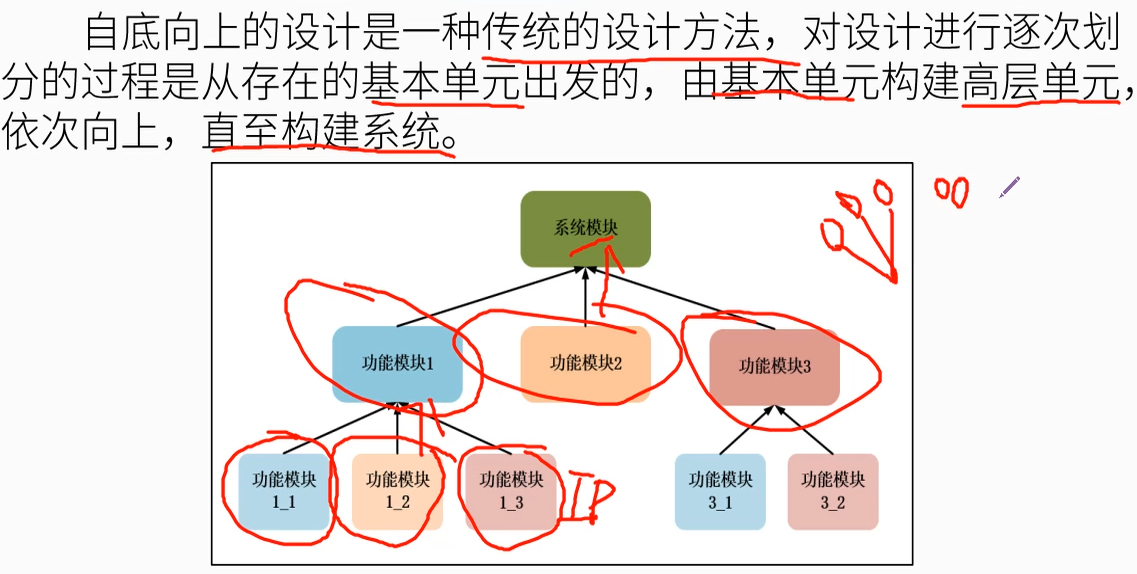

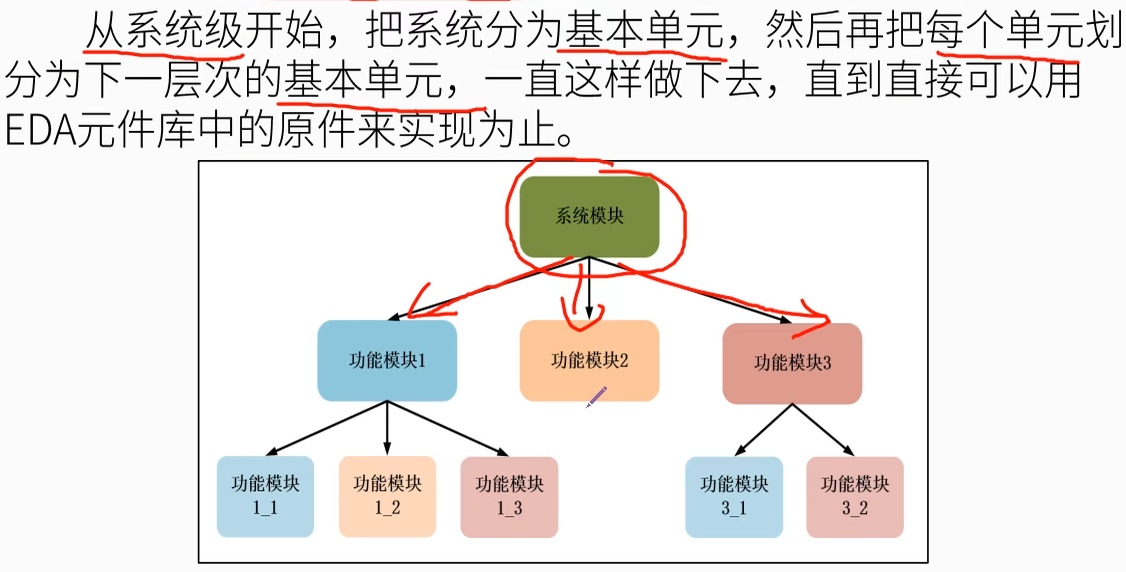

自底向上和自顶向下:

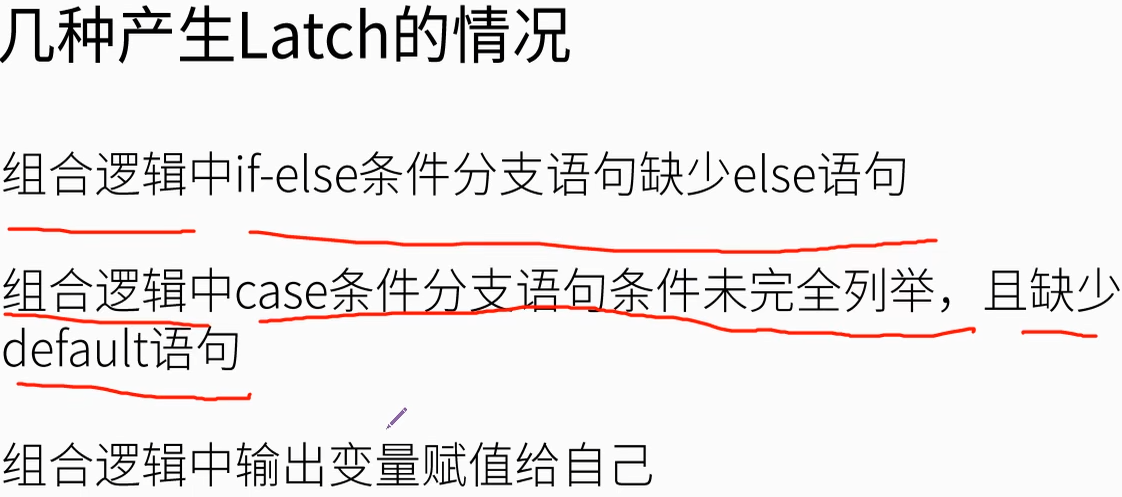

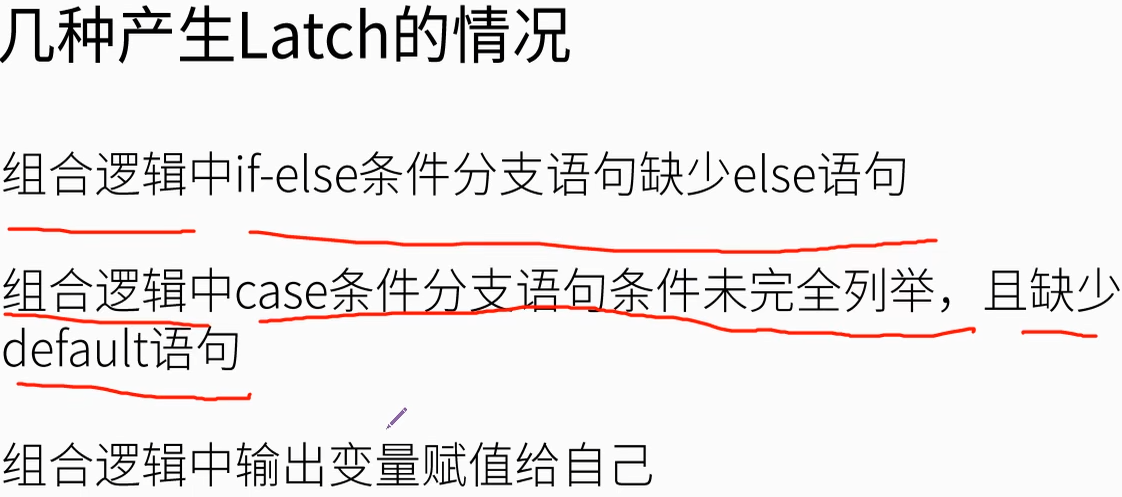

避免Latch产生

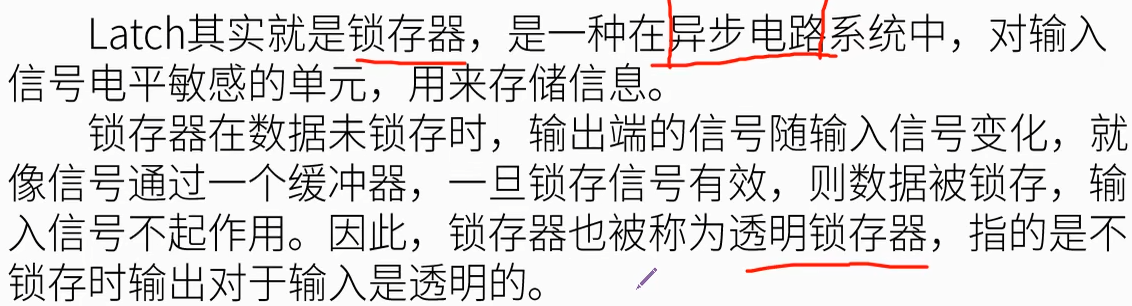

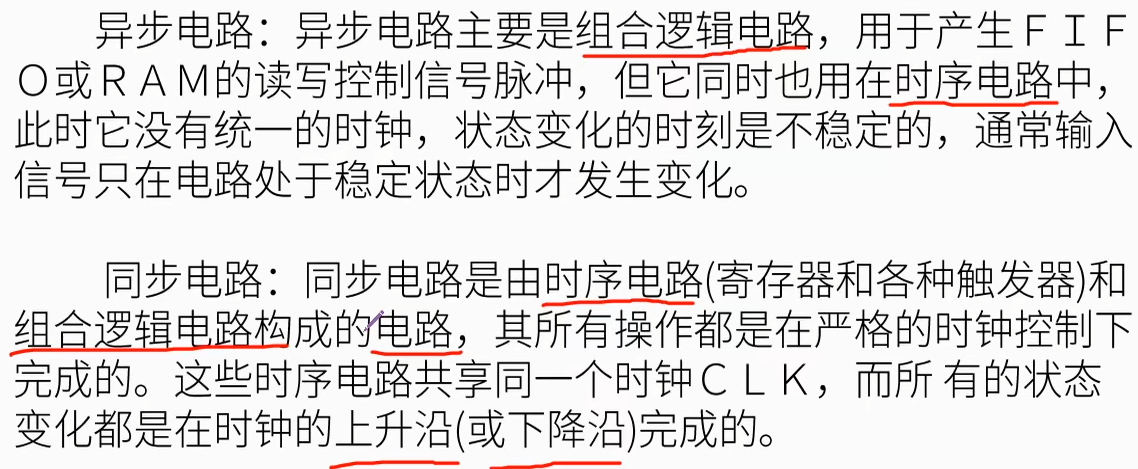

latch危害

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 Smartog!

流程:

自底向上和自顶向下:

latch危害