Xilinx IP核 以及 PLL

IP核

IP核是什么

IP(Intellectual Property)即知识产权。在半导体产业将IP核定义为“用于ASIC或FPGA中的预先设计好的电路功能模块”。简而言之,IP可以理解为电路功能模块。在数字电路中,将常用的且比较复杂的功能模块设计成参数可修改的模块,让其他用户可以直接调用这些模块。

为什么要使用IP核

IC的复杂度每年55%提高,设计能力每年提高20%左右。随着FPGA的规模越来大,它的设计也是越来越复杂,使用IP核可以提高开发效率,减少设计和调试时间,降低开发成本。

IP核的存在形式

分类依据:产品交付方式

- HDL语言形式——软核(软IP)

- 硬件描述语言,可进行参数调整、复用性强、布局、布线灵活、设计周期短、设计投入少。

- 网表形式——固核(PCIE接口内核,对时序要求比较严格的)

- 完成了综合的功能块;可预布线特定信号或分配特定的布线资源。预定义布局可能影响其他电路的布局。

- 版图形式——硬核

- 硬核是完成提供设计的最终阶段产品——掩膜(Mask);缺乏灵活性、可移植性差;更易于实现IP核保护。

IP核的缺点

- IP核往往不能跨平台使用

- IP核不透明,看不到内部核心代码

- 定制IP需要额外收费

Xilinx IP核的分类

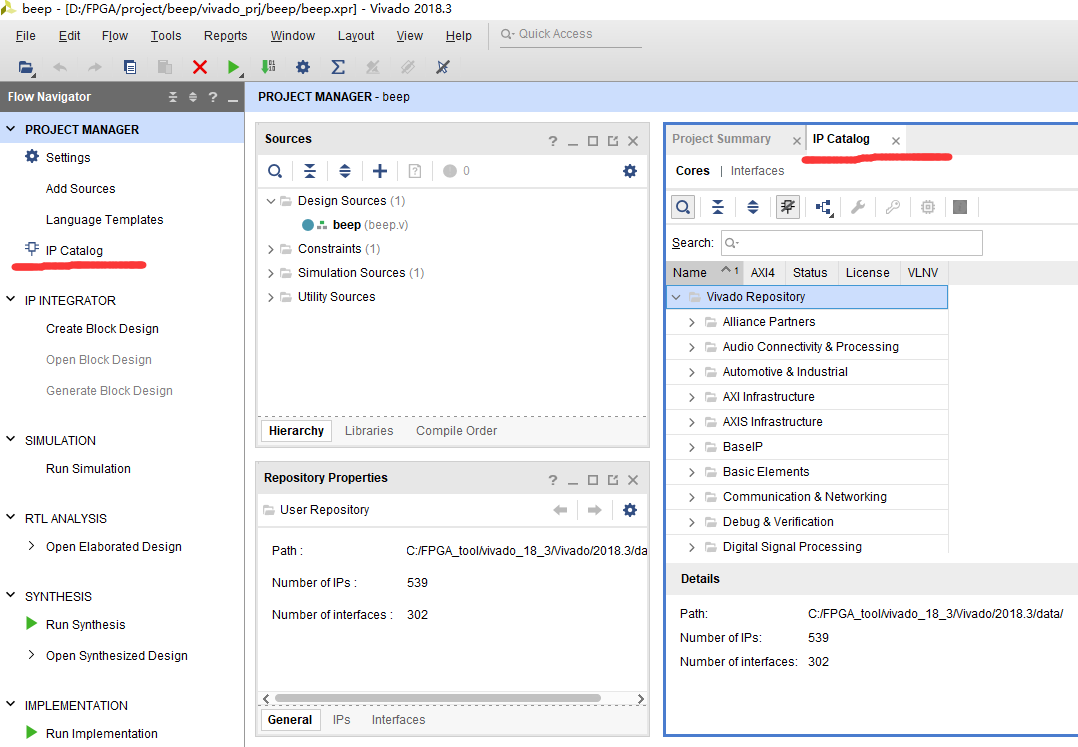

Xilinx IP核的调用

PLL IP核

PLL(Phase Locked Loop,即锁相环)是最常用的IP核之一,其性能强大,可以对输入到FPGA的时钟信号进行任意分频、倍频、相位调整、占空比调整,从而输出一个期望时钟。

模拟锁相环:稳定度高、相位、延时连续可调。温度过高、电磁辐射过强会失锁。还有数字锁相环。

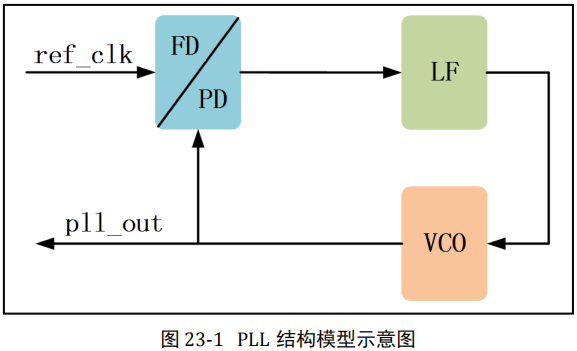

PLL基本工作原理:

基本工作流程:基本工作流程:①参考时钟ref_clk通过鉴频鉴相器(FDPD)和需要比较的时钟频率比较,如果参考时钟频率等于需要比较的时钟频率则FDPD输出为0,如果参考时钟频率大于需要比较的时钟频率则FDPD输出一个变大的成正比的值,如果参考时钟小于需要比较的时钟频率则FDPD输出一个变小的正比的值;②FDPD的输出连接到环路滤波器上,用于控制噪声的带宽,滤掉高频噪声,使之稳定在一个值,起到将带有噪声的波形变平滑的作用。FDPD输出的值越大,LF输出的电压越大;③经过环路滤波器的输出连接到压控振荡器(VCO)上,环路滤波器输出的电压可以控制 VCO 输出频率的大小,环路滤波器输出的电压越大 VCO 输出的频率越高,然后将这个频率信号连接到鉴频鉴相器作为需要比较的频率。如果 ref_clk 参考时钟输入的频率和需要比较的时钟频率不相等,该系统最终实现的就是让它们逐渐相等并稳定下来。如果 ref_clk 参考时钟的频率是 50MHz,经过整个闭环反馈系统后,锁相环对外输出的时钟频率 pll_out 也是 50MHz。

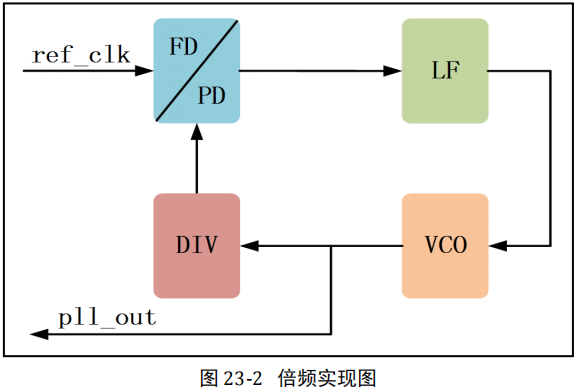

倍频工作思路:

倍频是在 VCO 后直接加一级分频器,我们知道 ref_clk 参考时钟输入的频率和需要比较的时钟频率经过闭环反馈系统后最终会保持频率相等,而在需要比较的时钟之前加入分频器,就会使进入分频器之前的信号频率为需要比较的时钟频率的倍数,VCO 后输出的 pll_out 信号频率就是 ref_clk 参考时钟倍频后的结果。

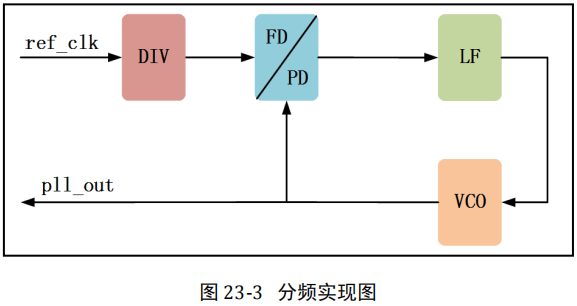

分频工作思路:

分频是在 ref_clk 参考时钟后加一级分频器,这样需要比较的时钟频率就始终和 ref_clk 参考时钟分频后的频率相等,在 VCO 后输出的 pll_out 信号就是 ref_clk 参考时钟分频后的结果。

IP核配置

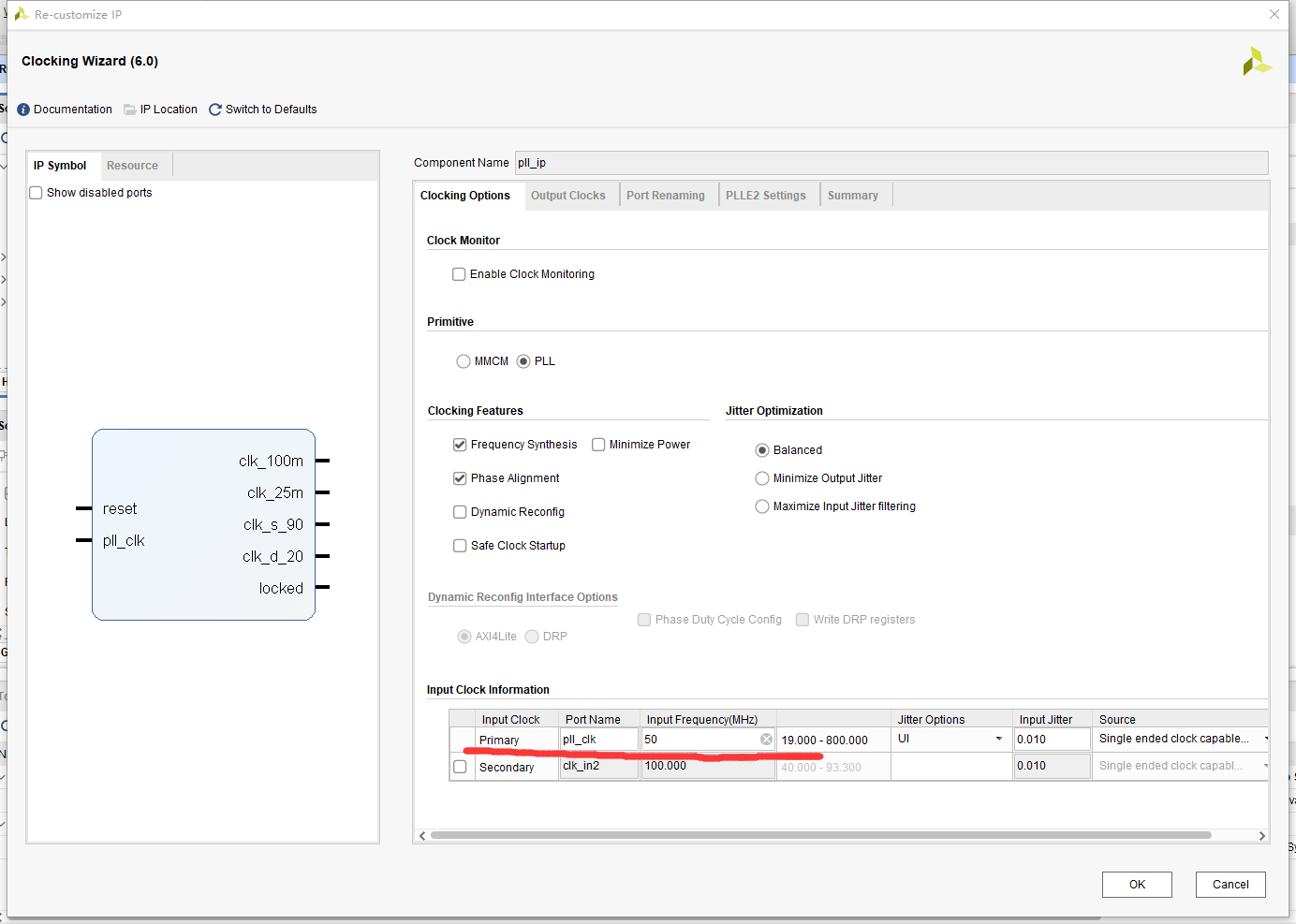

设置时钟输入参数

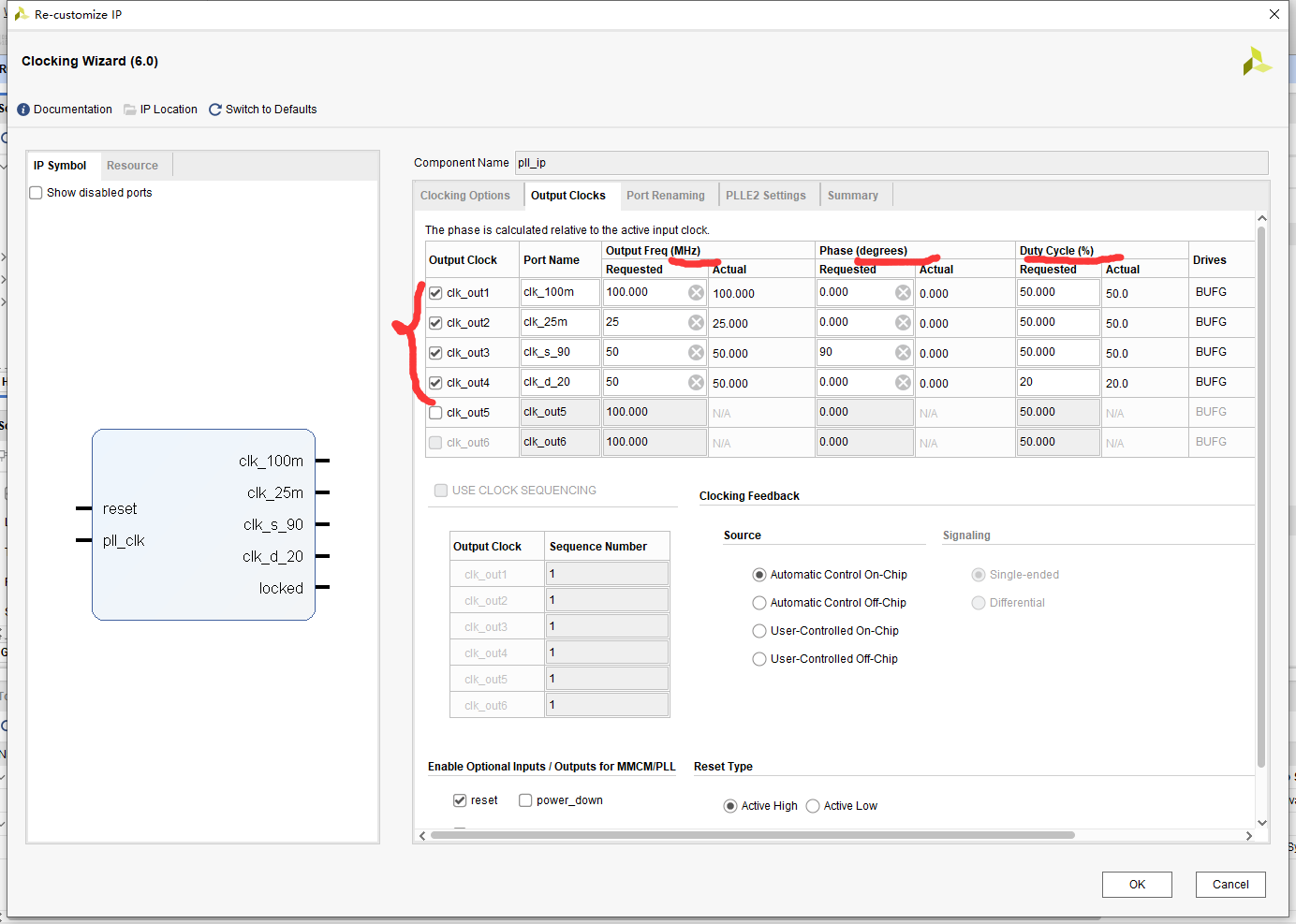

输出时钟数量,以及对应的频率、相位和占空比

IP核调用:

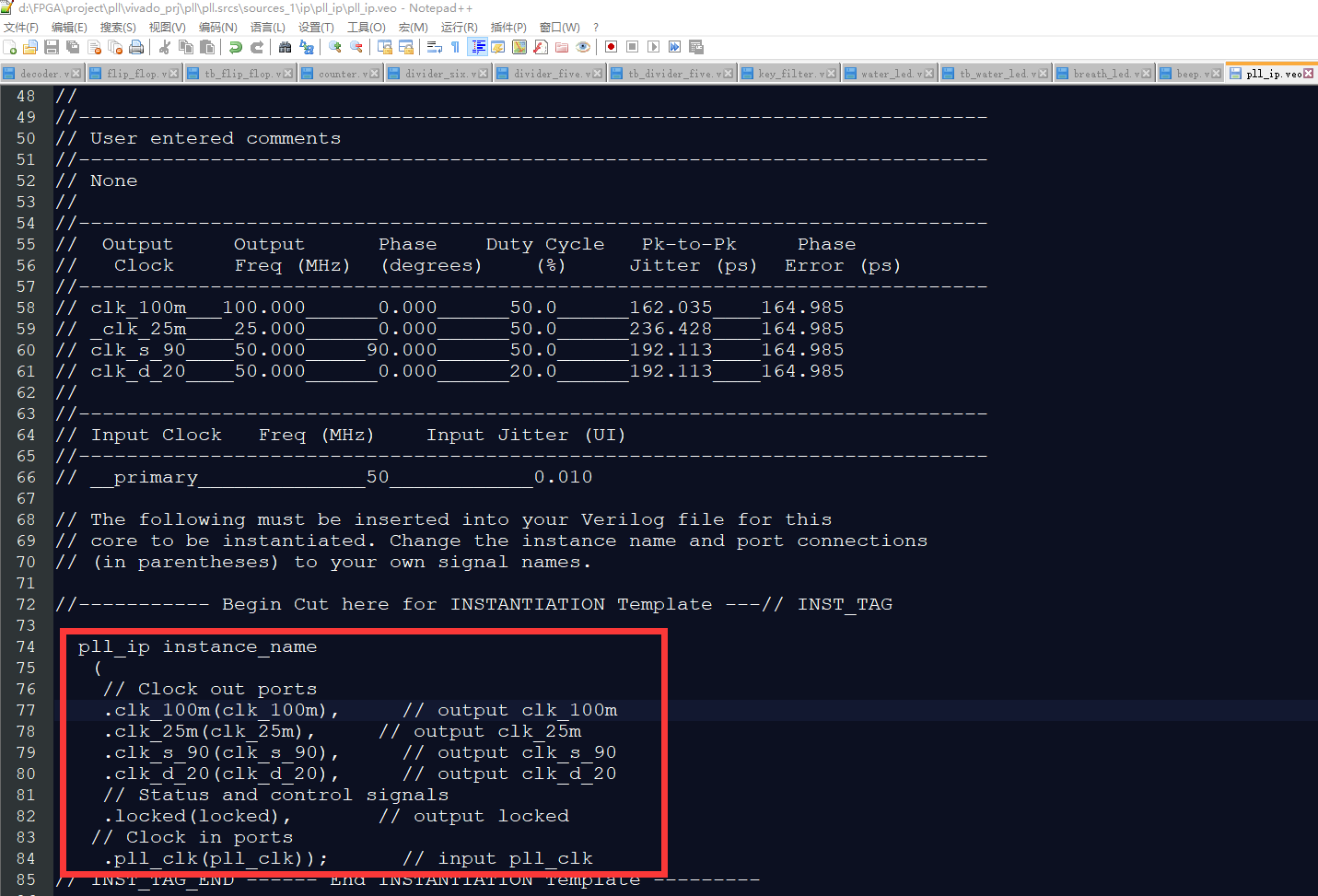

veo文件内有IP核例化模板

设计文件pll.v

1 | module pll( |

仿真代码tb_pll.v

1 |

|

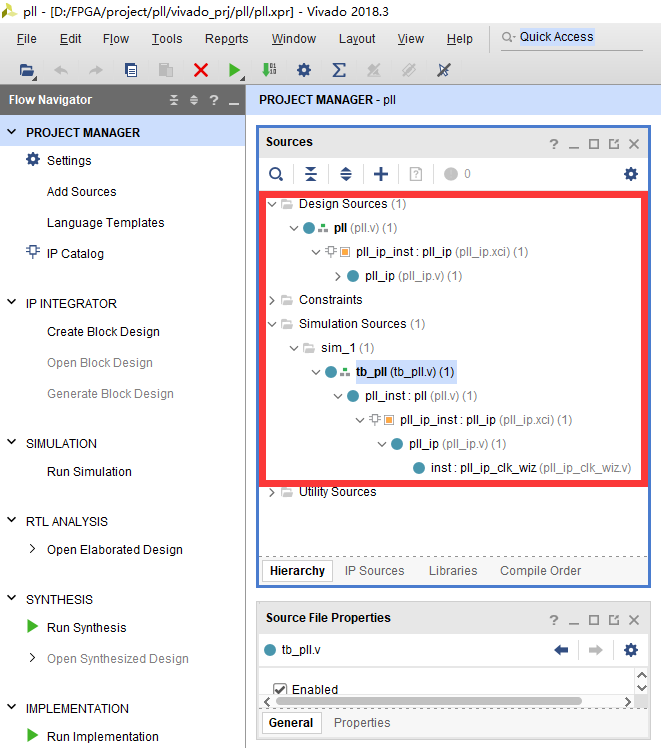

可以看到设计文件中实例化了pll_ip,仿真文件中也生成了调用关系

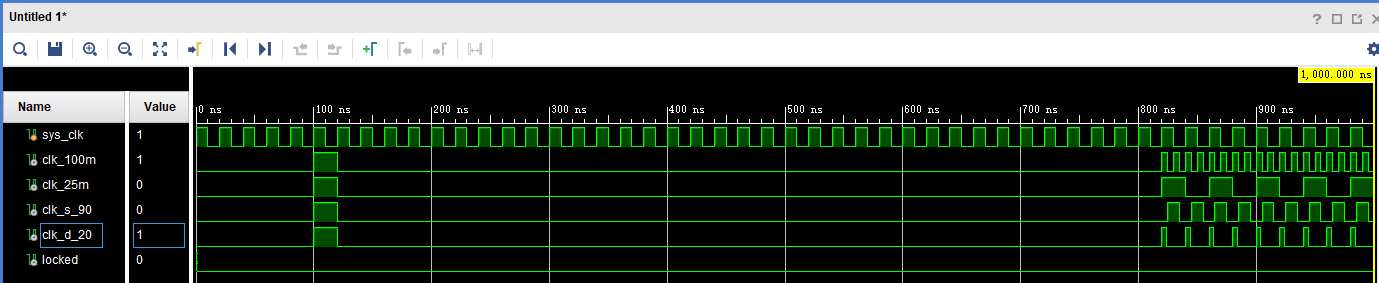

仿真结果: