Zynq UltraScale+ MPSoC Embedded Design Tutorial

结合两个教程:

1 Zynq vitis开发官网地址:https://xilinx.github.io/Embedded-Design-Tutorials/docs/2022.2/build/html/docs/Introduction/ZynqMPSoC-EDT/ZynqMPSoC-EDT.html

2 The_Zynq_Book_ZedBoard_Tutorials pdf

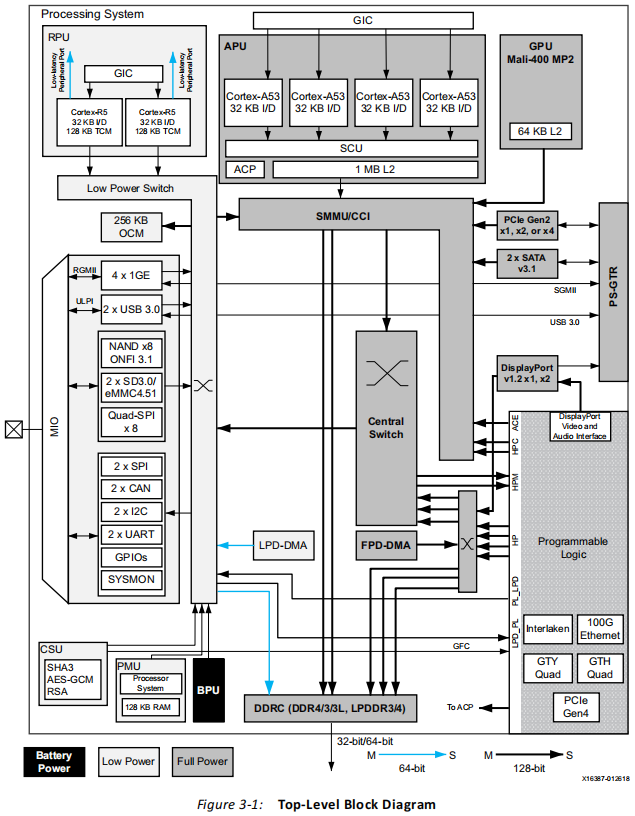

The Zynq UltraScale+ MPSoC PS block has three major processing units:

- Application processing unit: Quad-core Arm® Cortex™-A53 MPCore processors

- Real time processing unit: Dual-core Arm Cortex™-R5F MPCore processors

- Graphics processing unit: Arm Mali™ 400 MP2 GPU with pixel and geometry processor and 64 KB L2 cache.

- Platform management unit (PMU): Xilinx MicroBlaze™ based platform management unit

Vivado设计流程

在Vivado中,左侧的导航栏除了项目管理器,剩下的IP Integrator、Simulation、RTL Analysis、Synthesis、Implementation和Program and Debug功能分别如下。了解每个功能模块在整个开发流程中的作用有助于加深对项目的理解:

- IP Integrator:IP Integrator是Vivado中的一个工具,用于进行系统级集成。它提供了图形化的界面,用于将不同的IP核和设计模块进行连接和配置,以构建整个系统的设计。IP Integrator简化了设计流程,使得设计人员能够更轻松地实现复杂的系统集成。

- Simulation:Simulation(仿真)是在Vivado中进行功能验证和验证设计正确性的过程。它使用测试向量或仿真测试台来模拟设计的行为,以验证设计的功能和预期行为。仿真功能允许设计人员在实际部署之前对设计进行验证和调试。

- RTL Analysis:RTL Analysis(RTL分析)是Vivado中的一个工具,用于对RTL(Register Transfer Level)设计进行分析。它可以对设计进行时序分析、资源占用分析、时钟域分析等,以评估设计的性能、资源利用和时序要求。

- Synthesis:Synthesis(综合)是将RTL设计代码转换为门级网表的过程。在Vivado中,Synthesis工具会将设计描述转换为适合目标FPGA设备的门级网表,同时应用优化技术以提高电路性能和资源利用。

- Implementation:Implementation(实现)是在综合后执行物理布局、布线和时序优化等操作的过程。在Vivado中,Implementation工具会将综合后的门级网表进行物理布局和布线,同时进行时序分析和优化,以满足设计的时序约束和目标设备的资源利用。

- Program and Debug:Program and Debug(编程和调试)是将生成的比特流文件加载到目标FPGA设备上并进行调试的过程。在Vivado中,Program and Debug功能允许设计人员将设计通过JTAG或其他接口编程到FPGA设备,并使用调试工具进行调试、观察信号和验证设计的功能和性能。

这些功能在Vivado中代表了设计流程的不同阶段和操作,从系统级集成到仿真、分析、综合、实现和调试,帮助设计人员完成设计的各个方面,并确保设计的正确性和性能。

vivado中各个文件类型及作用:

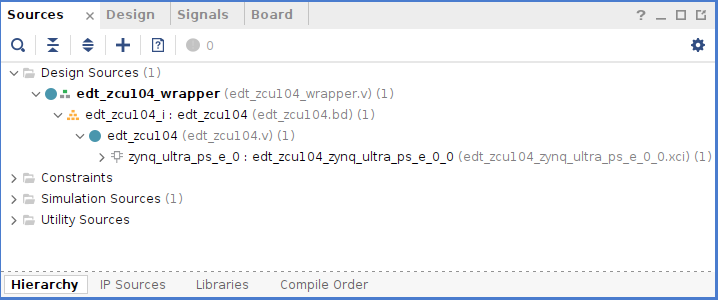

source里边可以看到.v、.bd、.xci文件

- .v文件: .v文件用于存储和描述硬件描述语言(Verilog HDL或VHDL)的代码,描述电路的逻辑行为和结构。这些文件包含了电路的逻辑描述,包括组合逻辑、时序逻辑、模块定义和信号连接等。

- .bd文件: .bd文件也是Vivado中的Block Design文件,用于描述和定义Block Design设计。用于图形化地构建FPGA设计,包括设计模块、IP核、连接关系和参数设置等。.bd文件通常是一个设计模块的Block Design,可以在更大的设计中进行复用。(在xsa中出现的叫bda文件)

- .xci文件: .xci文件是Xilinx IP核的配置文件,包含了IP核的配置参数和选项。它用于设置IP核的功能、接口、寄存器等,并可以与其他设计模块进行关联和集成。.xci文件是IP核的可编辑配置文件,可以在Vivado中进行编辑和定制。

- .xdc文件: Xilinx Design Constraints(约束)文件,用于指定和定义设计中的各种约束条件。这些约束条件包括时序约束、管脚约束、时钟约束等,以确保设计在实现和运行时满足特定的要求。.xdc文件是一个文本文件,包含了约束的语法和语义,可以在设计过程中手动编写或自动生成。

- .xpr文件:.xpr文件是Vivado项目文件的扩展名,它包含了整个Vivado项目的设计和配置信息。.xpr文件是一个综合的归档文件,包含了设计文件、约束文件、IP核配置、工具设置和生成比特流文件等信息。通过打开.xpr文件,可以恢复和管理完整的Vivado项目。

- .xsa文件: 在vivado中file—Export—Export Hardware生成,.xsa文件是Xilinx System Archive的缩写,是Vivado中用于保存和共享整个项目的设计和配置信息的文件。.xsa文件是一个归档文件,包含了设计文件、约束文件、IP核配置和生成比特流文件等。通过.xsa文件,可以在不同的Vivado环境中加载和重建整个项目。

Vitis ZYNQ开发

Creating a New Embedded Project with Zynq UltraScale+ MPSoC

创建一个Zynq PS系统作为嵌入式顶层设计

Design Input and Output files:项目不需要任何输入输出,我们将创建一个MPSoC的PS系统,不会用到任何的PL IP资源,所以项目不需要经历implementation和bitstream generation阶段。

Starting Your Design:创建一个RTL项目,选择目标开发板。

Creating a Block Design Project:在Vivado IP integrator对话中创建Block Design,添加想要使用的IP核,这里只用到了Zynq 的PS端,所以只添加了 Zynq UltraScale+ MPSoC IP资源。

Managing the Zynq UltraScale+ Processing System in Vivado:双击添加的PS IP核,可以看到内部的各种资源,和官方提供的文档中的资源图基本一致。

默认情况下PS没有任何外设连接。退出IP资源查看窗口,Run Block Automation 提示可以自动连接资源。点击 Run Block Automation ,接受默认的处理器系统选项并进行默认的引脚连接。

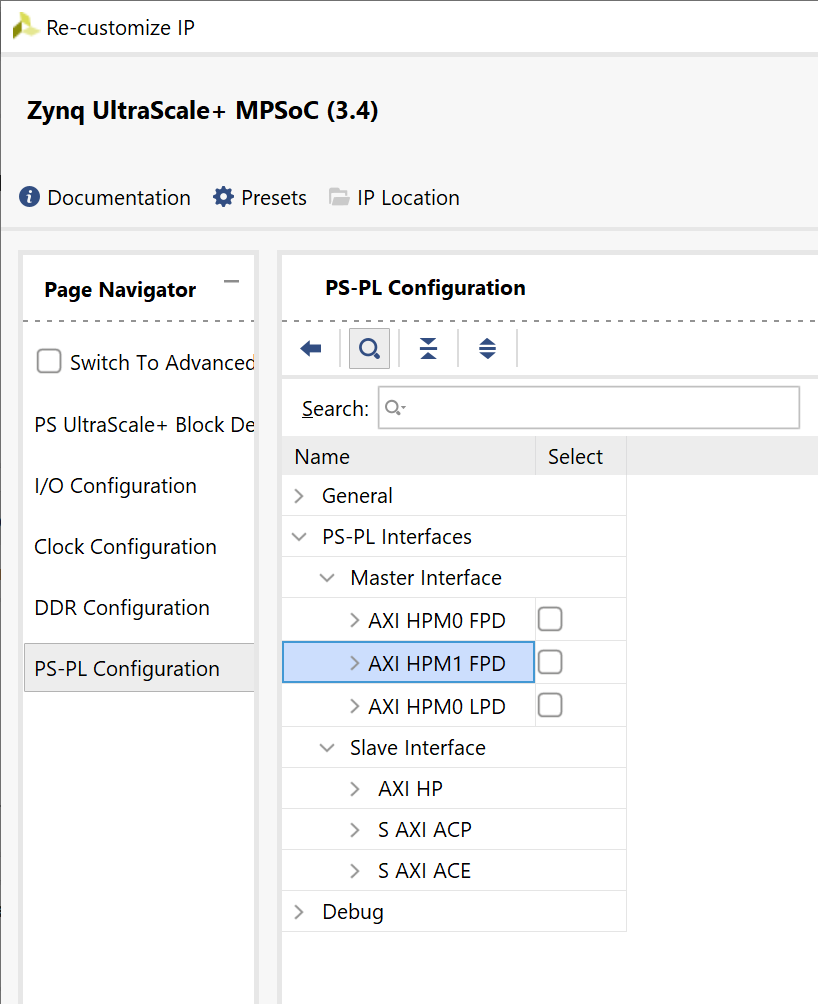

再次点击PS IP核,可以看到内部✔的资源已被使用。点击绿色IO外设,可以看到具体的资源配置界面:IO外设、Clock、DDR配置、PS-PL配置。

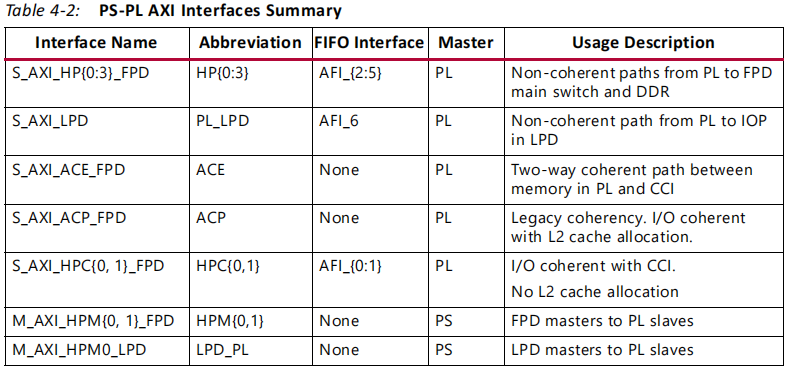

由于教程不适用PL资源,可以将PS-PL configuration中的AXI HPM0 FPD and AXI HPM1 FPD高速数据传输和通信接口取消勾选(通过这两个高性能主设备接口,PS可以与PL中的IP核进行高速数据交换,实现复杂的数据处理、协同计算或加速计算等应用)。其他接口的作用:

Validating the Design, Creating the Wrapper, and Generating the Block Design:块设计提供所有 IP 配置和块连接信息。 Vivado 可以在运行综合和实现之前验证模块设计。如果设计有错误,这可以帮助节省时间。 验证后,从模块设计生成源文件,以便合成器可以使用和处理它们。 您还需要为模块设计生成包装器,因为 Vivado 要求设计顶层是 HDL 文件。

- Block Diagram图中右键点击Validate Design或者F6。在Block Design——Hierarchy中右键edt_zcu104,选择Create HDL Wrapper。选择Let Vivado Manage Wrapper and auto-update,点击OK,将生成edt_zcu102_wrapper。

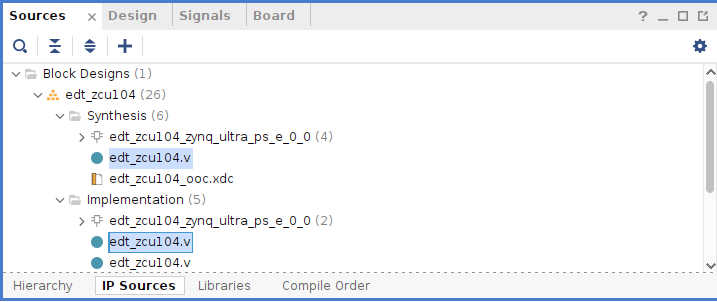

- Flow Navigator -> IP INTEGRATOR中选择Generate Block Design,选择Global,点击Generate.选择“ Generate Output Products”时,Vivado 工具会自动生成处理器子系统的 XDC 文件(XDC文件提供时序约束、管脚约束、时钟约束、约束检查)。

- 生成完成后,点击OK,点击IP Sources,可以看到Generate Block Design的输出结果。

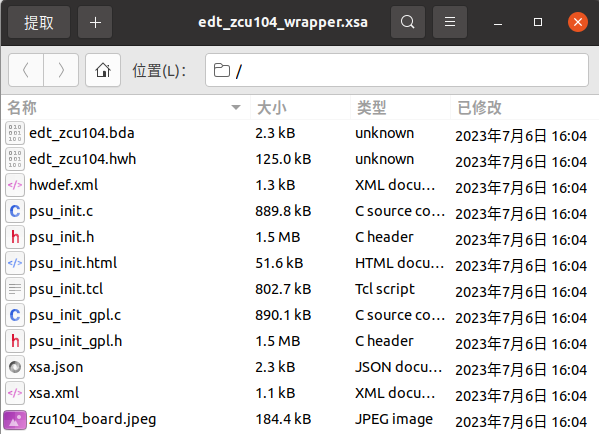

Exporting Hardware:在vivado顶部的菜单栏选择File→ Export → Export Hardware,点击Next。在输出窗口选择Pre-synthesis、点击next。输出XSA文件名、输出路径,点击next。单击“finish”,在指定路径下生成硬件平台.xsa文件。它将作为下一个示例的输入文件。

- 对于嵌入式设计而言,pre-synthesis XSA 和post-implementation XSA的区别在于是否包含bitstream文件。如果在 Vitis IDE 中运行应用程序,可以在运行应用程序之前将比特流配置到硬件。如果在xsa文件中存在bitstream文件,vitis会默认使用它。如果不包含bitstream文件,或者想使用其他的bitstream文件,可以在vitis IDE中指定bitstream路径。

- XSA中的文件

Building Standalone Software for PS Subsystems

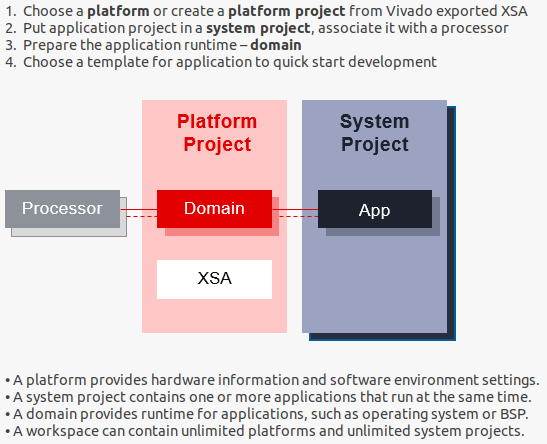

上边我们将目标平台的硬件设计导出了XSA,如上图所示,里边包含了硬件Block设计和描述、PS系统初始化、以及Bitstream(如果有的话)。现在我们把生成的XSA文件导出到Vitis IDE中。

我们将完成以下实验:

- 从XSA中创建平台项目。第一阶段引导加载程序 (FSBL) 和 PMU(平台管理单元)的 PMU 固件将作为该平台项目中的引导组件创建。通过PMU的功能和控制,Zynq芯片的处理系统部分能够进行有效的电源管理、温度监测、时钟管理和重置控制。

- 为应用程序处理单元 (APU) 创建裸机应用程序。

- 为 APU 和实时处理单元 (RPU) 创建系统项目。

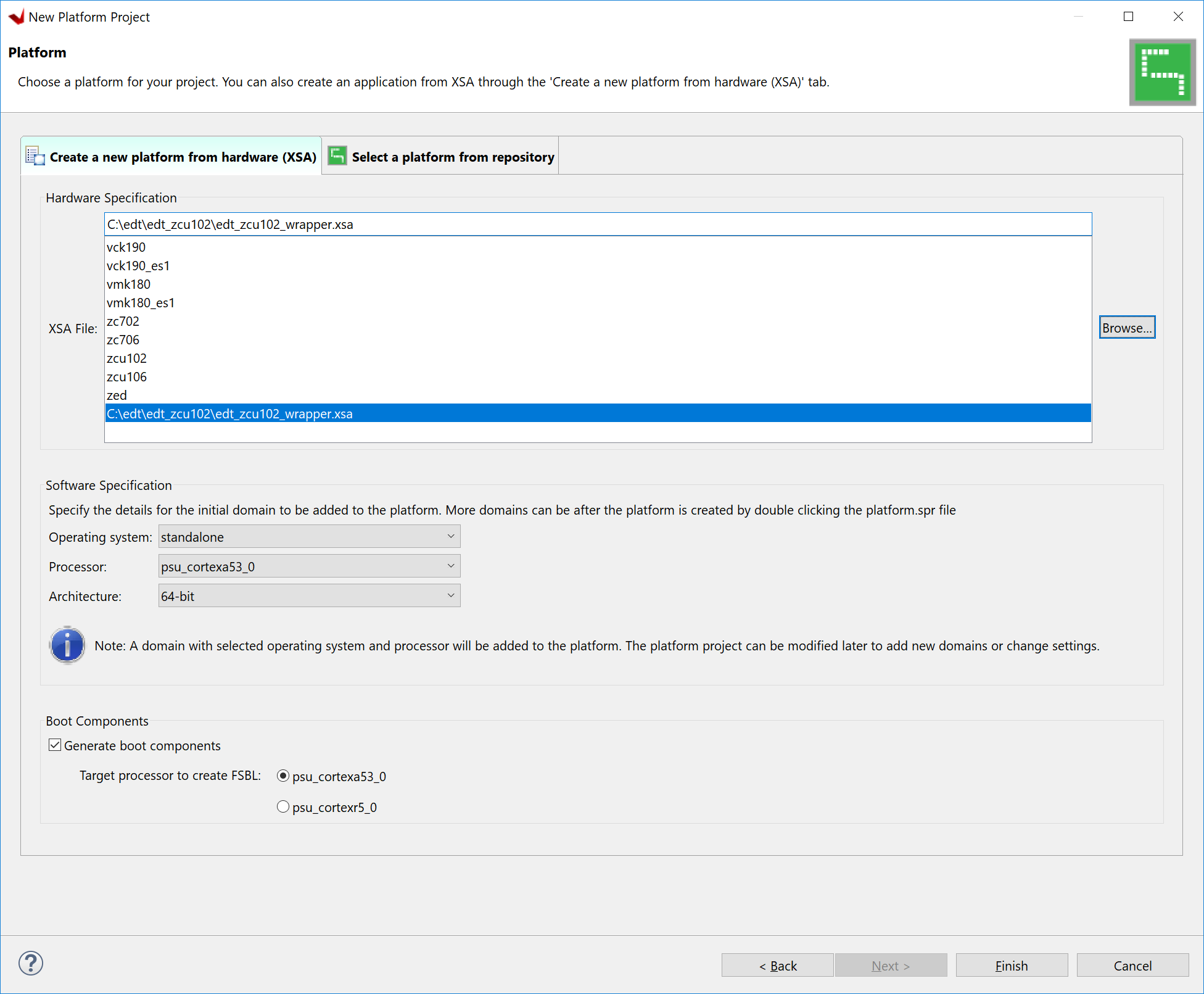

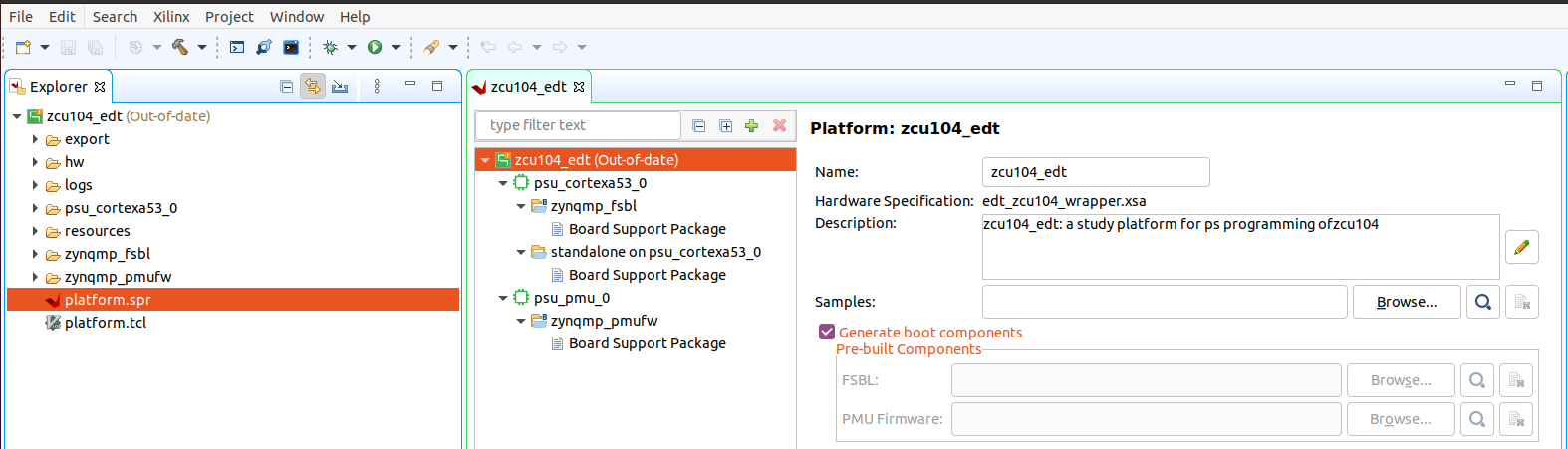

Example2 Creating a Platform Project Using Vitis IDE

描述:我们要创建一个platform项目,项目会从XSA文件中读取硬件信息,并包含前文提到的PS中各处理单元的运行时环境。开发的软件应用程序可以连接到这个平台项目生成的各个Libraries库。

输入: hardware handoff XSA file (edt_zcu102_wrapper.xsa)

输出:Standalone BSP libraries for Arm Cortex-A53、Boot components (FSBL: zynqmp.elf and PMUFW: pmufw.elf)

首先在Arm Cortex-A53上创建一个standalone domain。

点击finish,vitis将生成platform。可以看到有下面domain:

构建项目。右击platform项目,点击build project。项目构建过程构建standalone BSP、FSBL 和 PMUFW。 FSBL 和 PMUFW 有自己的 BSP。构建过程需要一些时间。构建完成在每个domain下会生成一些.c .o文件。

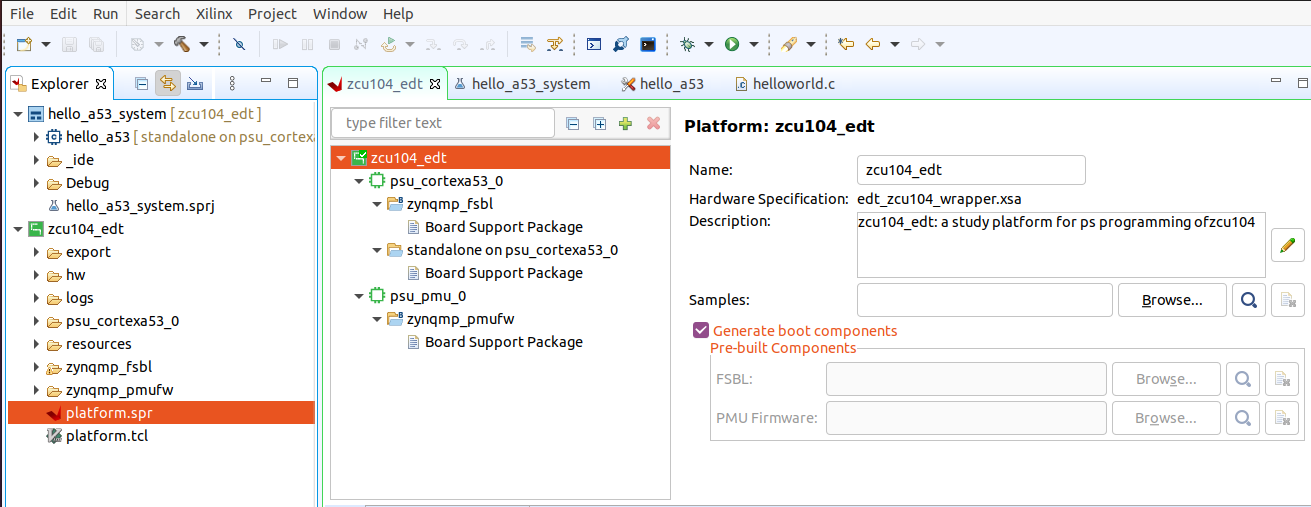

Example3 Running the “Hello World” Application from Arm Cortex-A53

描述:在构建的platform基础上创建“hello world”应用程序。将学习如何管理电路板设置、进行电缆连接、通过 PC 连接到电路板,以及使用 Vitis IDE 中的系统调试器在 JTAG 模式下从 Arm Cortex-A53 处理器运行简单的“Hello World”软件应用程序 。

输入:上一步platform构建生成的standalone BSP libraries

输出:针对 Arm Cortex-A53的hello.elf(.elf 文件是将源代码编译成可执行文件后的结果,它在嵌入式系统和 FPGA 开发中起着关键的作用,用于直接运行程序、调试代码以及进行板级验证和集成测试。)

连接电源、jtag usb线、设置开发板JTAG启动模式

右键file选择File → New → Application Project,next,随后如下操作。随后点击finish。

| Screen | System Properties | Settings |

| —————————————- | ———————————————- | ——————————————- |

| Platform | Select platform from repository | zcu102_edt |

| Application project details | Application project name | hello_a53 |

| | System project name | hello_a53_system |

| | Target processor | psu_cortexa53_0 |

| Domain | Domain | standalone on psu_cortexa53_0 |

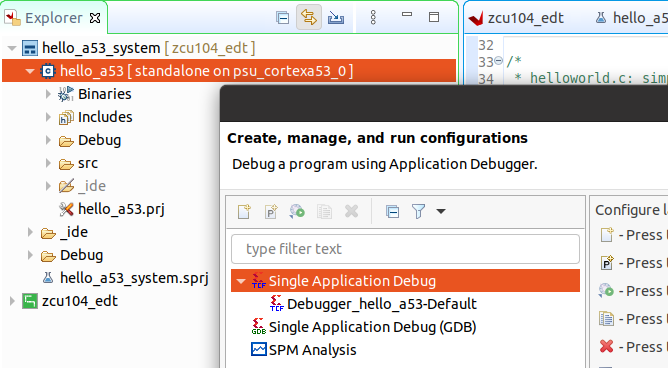

| Templates | Available templates | Hello World |运行 hello world程序:先右击hello_a53_systrem,选择build project,在右键下面的hello_a53,Run as → Run Configurations 然后 右击 Xilinx Application Debugger 选择 New Configuration,自动生成的

Debugger_hello_a53-Default,点击Run.

Jtag接口应该会输出hello world等信息。在 Zynq UltraScale 评估板上执行上述软件应用程序无需下载比特流。 Arm Cortex-A53 四核已存在于处理系统中。 该系统运行简单应用程序的基本初始化是通过设备初始化 Tcl 脚本完成的。

1

2

3

4

5

6Xilinx Zynq MP First Stage Boot Loader

Release 2022.2 Jul 7 2023 - 01:08:55

PMU-FW is not running, certain applications may not be supported.

Hello World!!

Successfully ran Hello World application

********end********

一些概念:

Domain:可以是standalone BSP、Linux OS、第三方OS如FreeRTOS。我们可以创建多个应用程序在domain上运行。domain与平台中的单个处理器或同构处理器集群(例如:A53_0 或 A53)关联。

Board Support Package:板支持包 (BSP) 是给定硬件平台或板的支持代码,有助于在加电时进行基本初始化,并帮助软件应用程序在其上运行。

Standalone BSP:Standalone 是一个简单的低级软件层。 它提供对基本处理器功能(例如缓存、中断和异常)以及托管环境的基本处理器功能的访问。 这些基本功能包括标准输入/输出、分析、中止和退出。 它是一个单线程半托管环境

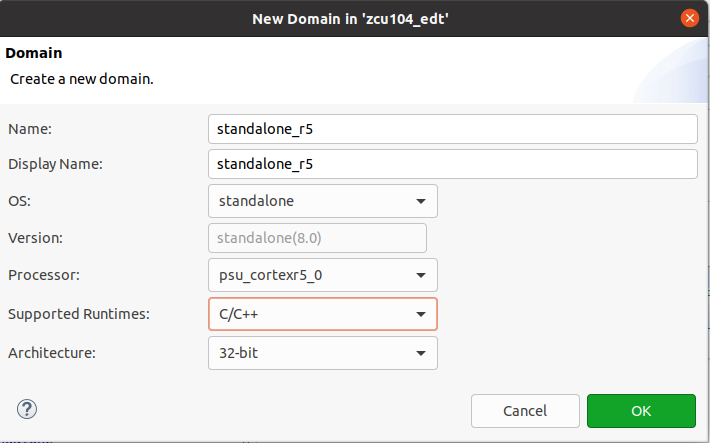

Example4 Running the “Hello World” Application from Arm Cortex-R5

描述:我们将在Arm Cortex-R5上运行hello world代码。同样的我们的platform中的PS系统包含了R5,所以我们首先要创建一个R5的Domain,然后才能创建运行在R5上的应用程序。

输入:zcu102_edt platform with standalone domain on Arm Cortex-A53

输出:zcu102_edt platform with standalone domain on Arm Cortex-A53 and Cortex-R5F processors

- 创建Arm R5的domain:首先我们点击platform project中的.spr项目文件,可以看到目前都有哪些domain。我们点击+创建一个新的ARM R5的domain,新的domain将出现在platform spr文件中。

创建R5的hello world程序:这里的步骤和之前类似,点击File → New → Application Project,选择之前的platform,输出application项目名称,选择Target processor为psu_cortexr5_0,domain为standalone_r5,选择hello world模板。创建application完成后,选择hello_r5_system,点击🔨图标构建项目。

在Arm 5上运行hello world代码:选择hello_r5,右键Run as → Run Configurations,右键Xilinx Application Debugger,New Configuration,将自动生成应用debug配置。点击Run,在Jtag窗口中将输出信息。

1

2

3

4

5

6

7Connected to /dev/ttyUSB3 at 115200

Xilinx Zynq MP First Stage Boot Loader

Release 2022.2 Jul 7 2023 - 01:08:55

PMU-FW is not running, certain applications may not be supported.

Hello World from r5

Successfully ran Hello World application

********end R5********

Example5 Using System Project to Manage Multiple Applications in the Vitis IDE

描述:Vitis可以将需要同时运行的项目组织在一个系统项目中。当Arm Cortex-A53, Arm Cortex-R5F, or MicroBlaze soft 处理器需要同时运行时,采用统一的系统组织方式进行Debug会很方便。这个例子我们将创建一个hello_system项目,这个项目包含运行在Arm A5上的hello world,同时包含运行在R5上的hello world。我们将修改“Hello World”应用程序源代码。 导入为 Arm Cortex-R5F 准备的源代码。 调整链接描述文件。

输入:(1)Platform: zcu102_edt with standalone domains for Arm Cortex-A53 and Arm Cortex-R5F;(2)Source code for Arm Cortex-R5F

输出:System project hello_system that includes hello_a53 and testapp_r5 applications

创建hello_system系统项目: 创建流程和example3类似,System project name为hello_system。Application project name为hello_sys_a53,修改helloworld.c代码。

1

print("Hello World from APU\n\r");

Arm A53为APU的处理单元。选择hello_sys_a53,点击编译,console将输出以下内容。hello_sys_a53.elf文件将在Debug文件夹生成。.elf文件是在Vitis中生成的可执行文件,用于存储已编译和链接的嵌入式软件程序。

1

2

3

4

5

6Finished building target: hello_sys_a53.elf

Invoking: ARM v8 Print Size

aarch64-none-elf-size hello_sys_a53.elf |tee "hello_sys_a53.elf.size"

text data bss dec hex filename

30300 2048 20668 53016 cf18 hello_sys_a53.elf

Finished building: hello_sys_a53.elf.size在同一系统项目中为基于 R5 的 RPU 处理单元创建自定义裸机应用程序:右键hello_system系统项目,选择Add Application Project,应用名为testapp_r5,Target processor为psu_cortexr5_0,Domain为standalone_r5,模板为Empty application(C)。在新建的testapp_r5应用导入官方提供的模板程序。

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22int main()

{

int Status;

//设置并初始化Uart

Status = PsUartSetup(&InterruptController, &UartPs,

UART_DEVICE_ID, UART_INT_IRQ_ID);

if (Status != XST_SUCCESS) {

xil_printf("UART Interrupt application Failed\r\n");

return XST_FAILURE;

}

while(1)

{//不断发送hello world消息,并在等待中断事件时进入低功耗状态

printf("\nHello World from R5-0 displayed on UART-1\n");

//警用异常中断

Xil_ExceptionDisable();

//这是一条汇编指令,表示将处理器置于等待状态,直到有中断事件发生

asm volatile ("wfi");

//重新使能中断异常

Xil_ExceptionEnable();

}

return XST_SUCCESS;

}修改 testapp_r5 的链接描述文件:当两个应用程序需要同时运行时,它们不能使用冲突的资源。他们不应该是彼此的记忆空间。他们应该使用自己的外围设备,或者按时间共享外围设备。在此步骤中,通过更新链接描述文件来分配内存空间。

- lscript.ld文件(或称为linker script)是链接器脚本文件,用于指定程序的内存布局和链接规则。链接器根据lscript.ld文件中的规则来决定代码和数据在内存中的分配和排列。

- 将psu_r5_ddr_0_MEM_0的起始地址和大小修改为0x80000000,0x10000000。编译testapp_r5。 成功后Debug文件夹将生成

testapp_r5.elf。

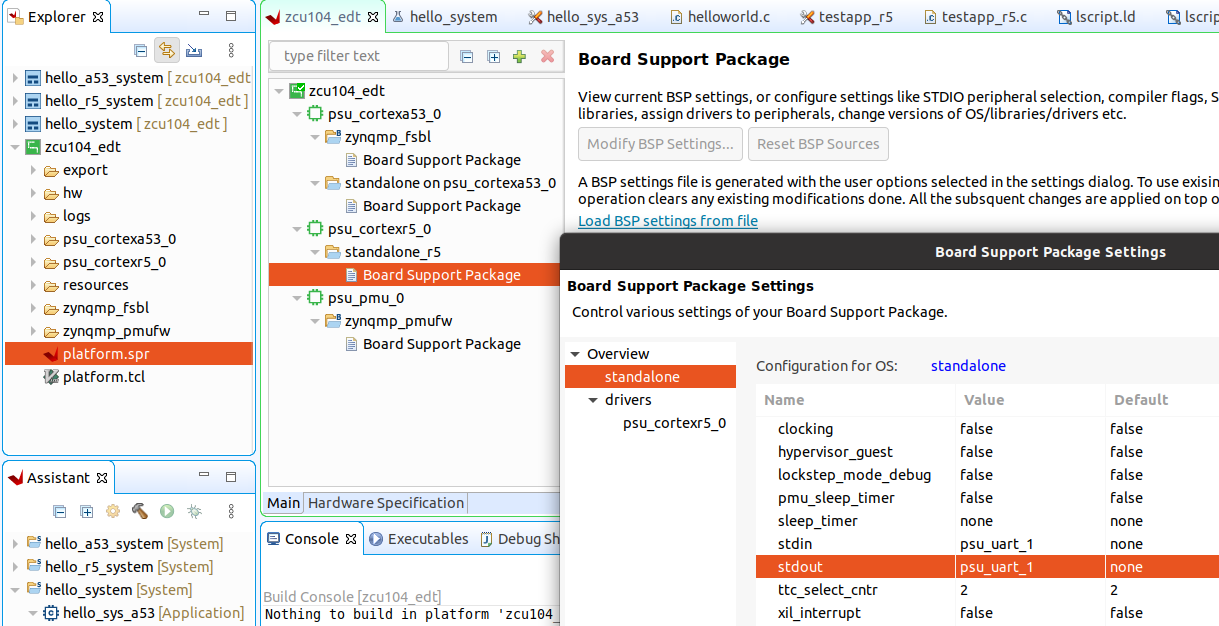

分配UART接口:ZCU104/2应该都有一个USB-TO-QUAD-UART Bridge IC,我们让A5用UART0,R5使用UART1,这需要对standalone_r5 bsp配置进行小修改。这里修改了R5 domain的stdin和stdout。

运行hello_system项目:右键hello_system,Run As → Launch Hardware,输出两个UART以及XSCT Console中可以发现fsbl.elf、hello_sys_a53.elf、testapp_r5.elf被成功下载。

Example6 Debugging Standalone Applications with the Vitis Debugger

描述:Vitis debugger能够查看程序执行时发生的情况。 您可以设置断点或观察点来停止处理器、单步执行程序、查看程序变量和堆栈以及查看系统中内存的内容。

右键hello_a53项目,Debug As→ Launch on Hardware → Single Application Debug.

Building and Debugging Linux Applications

关于如何利用vitis开发linux应用程序的内容见官网:

https://xilinx.github.io/Embedded-Design-Tutorials/docs/2022.2/build/html/docs/Introduction/ZynqMPSoC-EDT/6-build-linux-sw-for-ps.html

主要是使用PetaLinux创建Linux镜像和应用,主要内容为:

- Create a Linux boot image with PetaLinux.

- Create simple Linux applications with the Vitis IDE.

- Run and debug using the Vitis IDE.